-

-

TASKING

Altium TASKING embedded software ontwikkeltools geven u de technologie die u nodig heeft voor uw embedded applicaties.

-

-

-

fiXtress

fiXtress is een uitgebreide Design for Reliability (DfR) bundel. fiXtress is het enige hulpmiddel dat op schema niveau foutdetectie integreert met stress, thermische analyse en een voorspelling van levensduur uitvoert voordat er begonnen is aan de PCB lay-out.

-

-

-

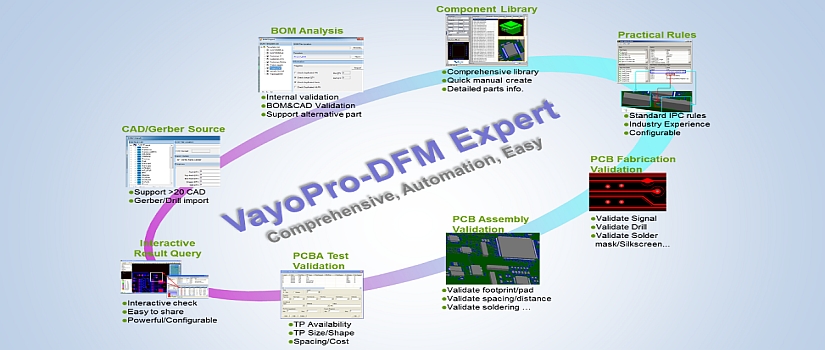

VAYO

VayoPro-DFM Expert is intelligente analyse software om nieuwe ontwerpen te analyseren op fouten.

-

-

-

BoardPerfect

BoardPerfect introduceert de volgende generatie routing met een resultaat die overeenkomt met handmatig gerouteerde ontwerpen.

-

-

-

Timing Designer

TimingDesigner® is de interactieve timing analyse oplossing om snel en accuraat uw elektronica ontwerp te analyseren.

-

-

-

ICD

De software van ICD kent 3 hoofdmodules: iCD Stackup Planner, iCD PDN (Power Distribution Network) Planner en iCD Coplanar Waveguide (CPW) Planner.

-

-

-

Hyperplot

IC ontwerpen worden steeds complexer en de bestanden zo groot dat ze niet meer uit te printen zijn. Dan wordt het tijd voor Hyperplot

-

-

-

Simplified Solutions

Simplified Solutions biedt u de mogelijkheid om uw EDA-omgeving te koppelen aan uw 3D MCAD/ECAD-omgeving.

-

-

-

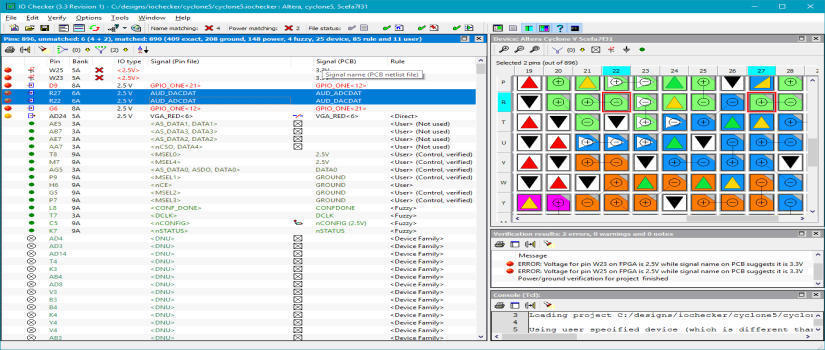

IO Checker

IO Checker maakt gebruik van regels (op basis van reguliere expressies) om de signaal namen van zowel de FPGA als CAD-omgeving te synchroniseren. Het verifiëren van meer dan 1000 FPGA IO-pinnen tussen PCB en FPGA gebeurd in minder dan 30 minuten.

-

-

-

JTAG Provision

Boundary-scan geeft u de snelste resultaten bij het testen en direct programmeren van uw elektronica ontwerpen.

-

-

-

JTAG Live

JTAG Live is de easy-to-use oplossing van JTAG Technologies voor het verifiëren van uw printed circuit board (PCB)

-

-

-

Altium Designer

Altium Designer brengt de ontwikkeling van PCB, FPGA, SoPC, Embedded Software en CAM output bijeen in één uniforme ontwerpomgeving.

-

-

-

Support

Heeft u vragen of problemen met één van onze software tools? Neem dan gerust contact met ons op!

-

-

Trainingen bekijk volledige agenda

-

-

07 apr 2025

-

Introductie tot VHDL

Deze training biedt een degelijke basis voor het gebruik van VHDL i.v.m. het ontwerp van complexe digitale ontwerpen.Inschrijven

-

-

-

08 apr 2025

-

Geavanceerde VHDL Ontwerptechnieken

Tijdens de training wordt de basiskennis opgefrist en zullen nieuwe aspecten van VHDL aan de orde komen.Inschrijven

-

-

-

09 apr 2025

-

Intel® Quartus® Prime Software: Foundation

De cursist leert hoe m.b.v. de Intel® Quartus® Prime software een FPGA of CPLD ontwerp kan worden ontwikkeld.Inschrijven

-

-

-

10 apr 2025

-

Introductie tot de Platform Designer Systeemintegratie Tool (Qsys)

Deze training leert u hoe u snel designs maakt voor Intel® FPGA's met gebruik van Platform Designer system integration tool (voorheen bekend als Qsys).Inschrijven

-

-

-

14 apr 2025

-

Ontwerpen met de Nios® II processor

Deze training leert u een Nios® II 32-bit microprocessor soft core te integreren in uw FPGA design.Inschrijven

-

-

-

17 apr 2025

-

Intel® Quartus® Prime Software: Timing Analysis with Timing Analyzer

Tijdens deze training leert u een design te begrenzen en te analyseren voor timing m.b.v. de timing analyzer in de Intel® Quartus® Prime Software.Inschrijven

-

-

-

12 mei 2025

-

Introductie tot VHDL

Deze training biedt een degelijke basis voor het gebruik van VHDL i.v.m. het ontwerp van complexe digitale ontwerpen.Inschrijven

-

-

-

13 mei 2025

-

Geavanceerde VHDL Ontwerptechnieken

Tijdens de training wordt de basiskennis opgefrist en zullen nieuwe aspecten van VHDL aan de orde komen.Inschrijven

-

-

-

14 mei 2025

-

Intel® Quartus® Prime Software: Foundation

De cursist leert hoe m.b.v. de Intel® Quartus® Prime software een FPGA of CPLD ontwerp kan worden ontwikkeld.Inschrijven

-

-

-

19 mei 2025

-

Introductie tot de Platform Designer Systeemintegratie Tool (Qsys)

Deze training leert u hoe u snel designs maakt voor Intel® FPGA's met gebruik van Platform Designer system integration tool (voorheen bekend als Qsys).Inschrijven

-

-

-

20 mei 2025

-

Ontwerpen met de Nios® II processor

Deze training leert u een Nios® II 32-bit microprocessor soft core te integreren in uw FPGA design.Inschrijven

-

-

-

27 mei 2025

-

Intel® Quartus® Prime Software: Timing Analysis with Timing Analyzer

Tijdens deze training leert u een design te begrenzen en te analyseren voor timing m.b.v. de timing analyzer in de Intel® Quartus® Prime Software.Inschrijven

-