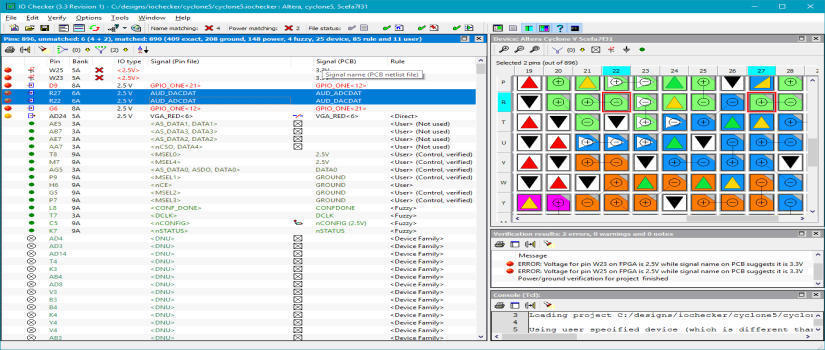

IO Checker

Verifying a 1000+ FPGA IO pins between PCB and FPGA in 30 minutes

When using placing a large FPGA on a PCB making sure that the FPGA pins are connected to the right signals on the PCB is a cumbersome task. On the FPGA side the pins are assigned to the HDL signals that form the top level of the logic implemented on the FPGA. On the PCB side the pins have to be connected to the proper net that will connect it to other components on the PCB. Because implementation of FPGA and PCB is often done in parallel and by different engineers, the signal names used are not always identical. To make things even worse, it is often necessary to perform pin swaps to prevent PCB routing problems. These pin swaps have to be made both on the FPGA and the PCB. As this is almost always manual work, and current devices have over 1500 pins, a mistake is easily made.

Intelligent Verification:

IO Checker uses rules (based on regular expressions) to match the signal names in both the FPGA and PCB design environment. It allows the tool to validate groups of matches although individual signals can still differ. The rules can be generated automatically and be fine-tuned by the designer. The automated approach will often match 80% to 90% of all device pins.

The flexibility of IO Checker allows it to be used in any design flow and does not require any design methodology. The rules generator in combination with the sorted problem view allows engineers to validate a 1000+ pins device in half an hour.

Once the project and its rules are defined it is a simple task to keep the FPGA and PCB data consistent. All out-of-date files are processed in one action and all changes are reported.

Features & Benefits:

- Compare FPGA and PCB pin names using regular expressions.

- Create & update FPGA constraint file.

- Automatic rule generation.

- Voltage checks for power pins.

- User directed acceptance of verified differences.

- One click verification and consistency.

- Reports incremental changes in pin- and net list.

- Concentrate on a dozen differences instead of a thousand lines.

- Fits in any design flow.

- HTML report

Explore IO Checker features:

- Signal view(s).

- FPGA Device (alternate) view.

- Intelligent Verification.

- Constraint file creation and update.

- Wiring FPGA symbols in a schematic diagram.

- FPGA Vendors and families.

- Supported PCB / Schematic capture systems.

- Supported platforms and operating systems.

Other IO Checker details:

- What is new in the 3.3 Release.

- What was new in the 3.2 Release.

- Platforms and licensing.

- Data Sheet (PDF)

More information:

For more information we like you to forward to the HDL Works website.